CDT编者按:该文在腾讯网、微信平台遭到删除,原因未知。

华为Mate 60 Pro搭载的麒麟9000S处理器将公众视线聚焦到了国产芯片制造之上。

跑分软件读取的数据、第三方拆解报告等诸多线索交叉显示,麒麟9000S是一颗7nm工艺芯片,它的产地清楚的标注这中国大陆,然而专用于生产7nm芯片的EUV早就于2019年对中国出口管制,中国的芯片代工企业只能获取到193nm光源的DUV光刻机,且这个出口管制的口子仍在不断收紧。日前,荷兰光刻机制造商ASML确认,到2024年将无法向中国客户交付DUV光刻机。

问题来了,这颗7nm芯片是如何生产出来的?

7nm工艺麒麟9000S的出现,大致有两种可能,一种是国产EUV光刻机实现突破,另一种是芯片制造商在DUV上,采用了特殊“魔法”,变相生产出了7nm工艺芯片。

从客观情况来看,后一种推测的可能性,要远远大于前一种,这一点在《中国芯片,只缺光刻机?》这篇文章中我也提到过,我们不单纯是缺光刻机,也包括它的配套,基础研究等突破,且即便EUV光刻机完成研发,到用于商用芯片的大规模量产,这个过程也不是一两年就能完成的事情。

所以本篇文章,我们将着重聚焦讲解用来生产28nm芯片DUV光刻机,为什么能够生产7nm芯片?以及顺便聊一聊为什么又说7nm,28nm这些工艺节点的命名是一个文字游戏。为了帮助大家理解,我们先从铺垫一下芯片制造相关的知识点,包括光刻原理、光刻流程。

01 重识光刻

用193nm的DUV(深紫外)光刻机,覆盖的是28nm及以上工艺节点,用DUV制造7nm工艺的芯片,这听起来是不可能完成的任务,因为商用的DUV光刻机光源的最短波长为193nm,与7nm有28倍的差距,看似无法突破,但业界确实用DUV制造出了7nm芯片,这是怎么实现的呢?

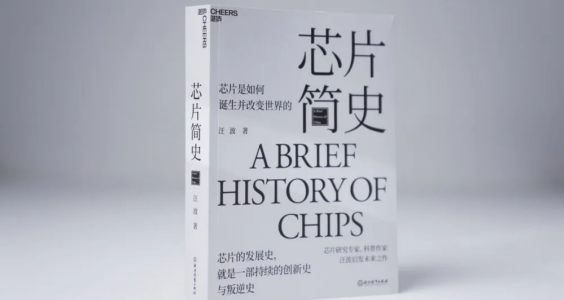

光刻的基本原理,红色为光刻胶,黄色为金属层,灰色为晶圆(衬底),图3上方为掩膜版

首先简要介绍一下光刻机的原理和芯片生产的光刻流程。光刻的原理跟传统胶片电影放映有点相似,放映电影是把图案从电影胶片透射到银幕上,而光刻则是将图案从掩膜版透射到晶圆表面,从而在晶圆表面上加工出特定的图案和线条(如上图)。

具体来说,首先是制作光刻所需的掩膜版,这相当于胶片。这需要将芯片版图用金属铬刻蚀到一种特殊的玻璃上,做出掩膜版。然后用紫外光透过掩膜版照射到下方的晶圆上。

掩膜版上的图案(也就是镀铬的部分)遮挡了一部分光线,而没有被遮挡的图案可以将光线透过去,这样电路图案就转移到了晶圆表面。而晶圆表面预先涂覆了光刻胶,被照射到的光刻胶发生化学反应,被化学溶液腐蚀清洗掉,露出了下方的晶圆,能被后续的工序刻蚀掉,从而在晶圆上加工出对应的图案和线条。

这样就可以一层一层加工出晶体管、金属互连线等芯片结构。

为了加工更小尺寸的晶体管,需要缩短紫外光的波长,这样照射在光刻胶上加工出来的线条才会更精细。

早期的紫外光的波长为436nm的g线,能加工工艺尺寸500nm以上的晶体管。随着晶体管尺寸继续缩小,光刻机上的紫外光源的波长缩短到了405nm的g线和365nm的i线。当晶体管工艺尺寸缩小到了250nm以下,对应需要紫外光源的波长缩短到248nm和193nm,也就是深紫外光(DUV)的范围。

02 “7nm”的文字游戏

其次要和大家强调一下,芯片制造商工艺节点的概念,也就是7nm、14nm、28nm等等,是晶圆制造厂为了标识芯片加工技术所起的一个名字或者规格。

20世纪90年代中后期,工艺节点是芯片厂能实现的晶体管栅极最小长度(线宽),简称栅长。但是现在的7nm工艺节点不真正等于数学上的7nm,在7nm工艺芯片上的每个晶体管尺寸都远大于7nm,“7nm”只是一个“标签”。

7nm之所沦为一个标签,离不开20世纪90年代以来半导体制造商制定的命名规范。

按照摩尔定律和登纳德缩小规则,每过一代栅长就缩小为上一代的70%,如果上一代晶体管的栅长是1微米,那么下一代是0.7微米,这样每个晶体管的面积刚好减半,或者让元件数量翻倍。

到了2005年,半导体制造厂发现,栅长无法按照每代减小为70%的节奏继续缩短,因为栅长越短,漏电流就越大,芯片过热问题就越严重。可是业界已经习惯了每次升级就乘以0.7的做法,于是半导体制造商不管下一代的栅长是否能缩小为70%,就直接将上一代工艺节点乘以0.7作为新的工艺节点,所以我们有了32nm、22nm、14nm、10nm、7nm等工艺节点名称。

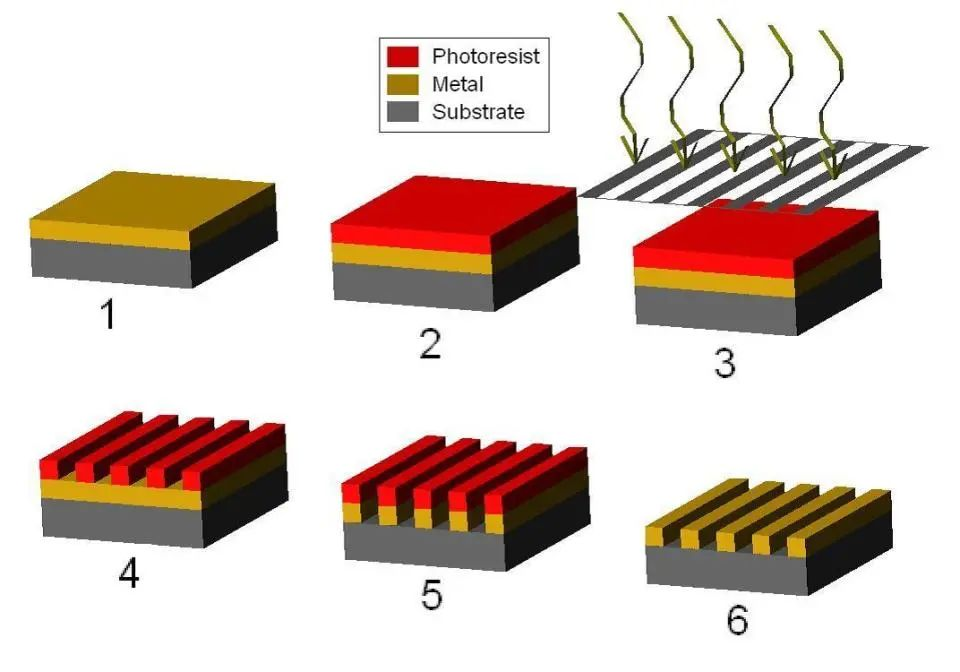

台积电的7纳米工艺:CPP=57nm,MMP=40nm

既然工艺节点无法真实地反映晶体管尺寸,那么业界用什么尺寸来表示晶体管大小呢?实际上,业界会用工艺栅间距(CPP)和金属间距(MMP)用两个尺寸来共同表示(如上图),它们相当于一个长方形的长和宽,二者的乘积决定了晶体管的面积。例如,台积电的7nm工艺栅间距(CPP)等于57nm,金属间距(MMP)是40nm。三星也差不多,这两个数据分别是54nm和36nm,都远远大于半导体制造厂所标称的7nm。

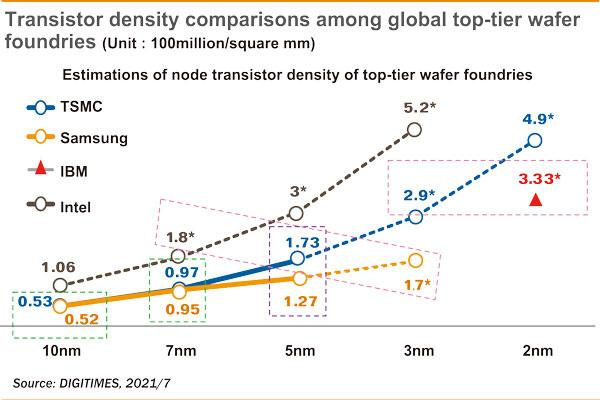

主要芯片制造商在不同节点上,对应的晶体管密度,英特尔、台积电和三星10nm节点,对应每平方毫米上的晶体管数量分别为106万、53万和52万。

过去英特尔比较实在,习惯用沟道长度(比栅长小)来定义节点,有说法是为了紧扣摩尔定律,不论原因如何,命名上总比竞争对手们吃亏。

比如,英特尔的10nm,晶体管密度比台积电和三星的7nm还要多(如上图),但从营销的逻辑来说,别人都说7nm,英特尔说自己是10nm,吃了个“没文化”的亏,所以后来英特尔也跟着对手们,改用intel 4、intel 3这样的节点命名方式。

上面阐释的这些,只是想告诉你,节点的命名,就是一个文字游戏,7nm工艺对应的最小金属间距在36nm-40nm左右。

有了这个认知,我们就可以来讲讲前面提到的193nm DUV光刻机,和要制造的7nm芯片之间的关系。或者这样说,DUV生产7nm芯片,实际上是利用193nm光源的光刻机,生产金属间距36nm-40nm的芯片。

193nm光源,和36nm的金属间距中间,差5倍左右,如何跨越这个差距?这里就不得不提DUV干式光刻机到DUV浸没式光刻机的迭代了。

DUV光刻机的光源波长虽然为193nm,但是光在水中会发生折射,波长则会缩短。193nm的紫外光在水中的折射率为1.44,波长为134nm。根据这一原理,林本坚在1987年提出了浸没式光刻,即在晶圆表面和透镜之间增加一层超纯水,让紫外光折射,从而将波长降低为134nm,2003年荷兰的ASML基于这项研究,第一个实现了浸没式光刻机。

从DUV干式光刻机到DUV浸没式光刻机,从193nm光源波长到134nm波长的紫外光,这与36nm的金属间距的差距再度缩小至4倍。

03 多重曝光搞定“最后一公里”

浸没式光刻机的出现,再次缩小了和“7nm”工艺的差距,但行业仍无法直接用这种光刻机加工出大家口中的“7nm”芯片,如果芯片制造商真要制造传闻的7nm麒麟9000S,双重曝光和多重曝光必不可少。

为了解释双重曝光技术,让我们举一个照相的例子。假设你是一个摄影师,要拍摄一幅运动会队列的照片,这个队列只有20个人,按照2米的间距站开,显得非常稀疏,怎么拍出40个人的感觉?你有一种解决方案,先拍完第一张,然后再让每个人平移1米,拍出另一张,随后通过软件,将两张照片合成在一起。

双重曝光技术也可以如法炮制。使用一组掩膜版,加工出间隔134nm的线条,再使用另外一组掩膜版,平移一段距离加工出另外一组间隔134nm的线条,二者组合起来,就有了间隔67nm的线条,这距离36nm又前进了一步。从22/20nm开始,业界开始导入双重曝光技术。

为了实现双重曝光技术,业界开发出了LELE法(光刻-刻蚀-光刻-刻蚀),它需要涂两次光刻胶,曝光两次,第一次曝光在硬掩膜上复制图形,第二次曝光在光刻胶上复制出最小线宽图案。但是由于使用两次曝光设备,大大推高了制造成本,花费的时间也更久。要知道光刻占整个制造时间的50%左右,增加一倍的曝光会大大延长整个制造时间。

为此,业界又开发出了效率更高的自对准双重图形化法(SAPD),这种方法将两次涂光刻胶减少到了一次,它利用化学气相沉积(CVD)技术将氧化硅沉积在第一次涂的光刻胶周围,自然地形成了对准后的加工位置,从而能实现第二次图形加工。

有了这些技术,双重曝光就能加工出67nm的金属间距,不过这距离36nm还差了两倍,怎么去突破最后的这2倍的差距?

有一个简单粗暴的方法,就是再做一次双重曝光,总共做四重曝光,就能再一次将67nm减半,加工出最小34nm的线条,刚好符合加工7nm所需的36nm的金属间距。

不过这个方法要付出的代价实在太大了,曝光时间是单重曝光的4倍,需要制备更多的掩膜版,每次曝光都需要更多的配套工序(光刻胶涂覆、软烘烤、对准、显影、甩干、硬烘烤、图形检测等),所需的全部制造工序从几百道增加到上千道,大大增大了制造的时间成本和物力成本。此外,曝光时间的增加会使镜头发热增大,温度升高又会导致镜头光路变形,套刻精度更难以控制,与之匹配的薄膜和刻蚀工艺难度也大大增加。还有,以上的计算没有考虑数值孔径(NA)对光刻精度的影响(这部分不涉及多重曝光的理解,故本文不对套刻精度、数值孔径详细展开)。为了提高数值孔径,还需要把镜头做得更大。

基于多重曝光技术,台积电于2016年6月开始用DUV生产7nm芯片(N7),三星则于2018年开始用DUV量产7nm芯片(7LPP)。至此,用DUV实现7nm工艺才成为现实。

一句话总结,虽然可以通过多重曝光的手段,利用193nm光源的DUV,生产7nm芯片,但时间、材料、人力成本都会大大增加,且由于工序极大的增加,良率也会受到影响。

作为对比,EUV的波长只有13.5nm,一次曝光就能做出7nm芯片,只不过EUV吊足了晶圆厂的胃口,直到2020年才正式在5nm工艺上使用。在此之前GlobalFoundry失去了耐心,宣布由于高昂的成本停止7nm技术的开发。

04 DUV能突破5nm工艺吗?

不过,这还不是故事的全部。

除了多重曝光技术,用DUV加工7nm工艺还需要很多技术的配合才能实现,包括相位移模板(PSM)、离轴光照、光学临近校正(OPC)、优化光圈和光刻图形(SMO)等,这几项技术催生了一门新的子学科:计算光刻。它所需的庞大数据使得英伟达的GPU芯片也成为了计算所需的工具,其推出cuLitho软件加速库,宣称可以将计算光刻的用时提速40倍。

之所以需要计算光刻,是因为当掩膜版上的线条变得很小时,紫外光通过掩膜版时会产生偏差,让光刻图形畸变。为此研究人员想到了一个方法,预先计算出掩膜版上可能的畸变,从而逆向地设计光刻所需的掩膜版的最佳形状,提前抵消这些畸变,这叫做逆向光刻计算,而这需要非常庞大的计算量,普通的计算机根本无力承担,研究人员不得不使用超级计算机和云计算。

与此同时,研究人员又将人工智能的机器学习算法应用到计算光刻上来。新一代的卷积人工神经网络被应用于光刻工艺模型、掩模优化、SEM数据处理等方面,而训练数据又需要庞大的GPU芯片组。除了器件层面的优化,研究人员甚至还将电路设计中要考虑的因素也融入到器件制造中来,在电路设计阶段就考虑对制造和光刻的影响,这叫做DTCO(设计与工艺技术协同优化),而这又需要EDA厂商升级算法和软件。

可以说,为了让DUV能制造出7nm工艺芯片,业界已经无所不用其极。下一步如果继续采用DUV制造5nm工艺芯片,四重曝光也不够了,需要6-8重曝光,以及更多的掩膜版,更长的光刻时间,更高的物力成本,这已成为不堪忍受之重。所以5nm芯片出来时,刚好EUV光刻机也准备好了,才将业界从繁琐的多重曝光下解脱出来,而7nm工艺也成为目前业界使用DUV制造出来的最后一代工艺。

关于作者:

《芯片简史》 作者:汪波 2023出版 ,*作者汪波博士是芯片研究专家,科普作家,在华为公司、法国里昂纳米国家实验室和北京大学深圳研究生院有二十多年的研究和教学经验,著有《芯片简史》、《时间之问》和《时间之问·少年版》,其中《芯片简史》入选2023年“南国书香节”十大好书榜,探照灯好书、第三期“新发现·科普书单”、百道网2023上半年影响力图书、中国传媒出版商报2023二季度影响力书单。